## DC Biasing Circuits of JFETs

### 1. Fixed-Bias Configuration:

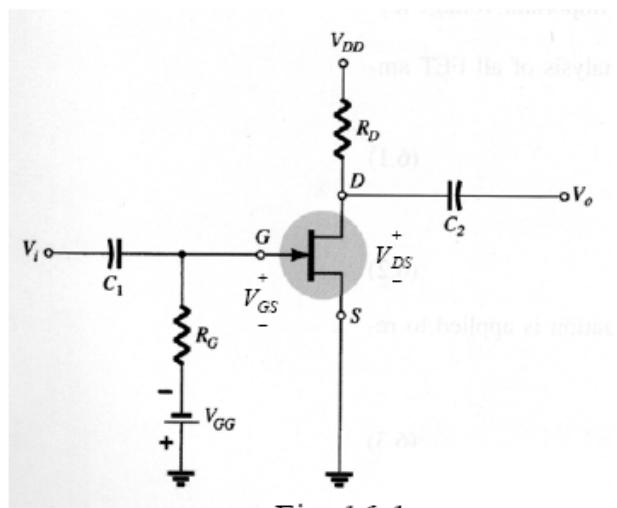

For the circuit of Fig. 16-1,

$$I_G \approx 0A,$$

and  $V_{R_G} = I_G R_G = 0V$ .

For the input circuit,

$$-V_{GG} - V_{GS} = 0,$$

and  $V_{GS} = -V_{GG}$

From Shockley's equation:

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

For the output circuit,

$$V_{DD} - I_D R_D - V_{DS} = 0,$$

and  $V_{DS} = V_{DD} - I_D R_D$

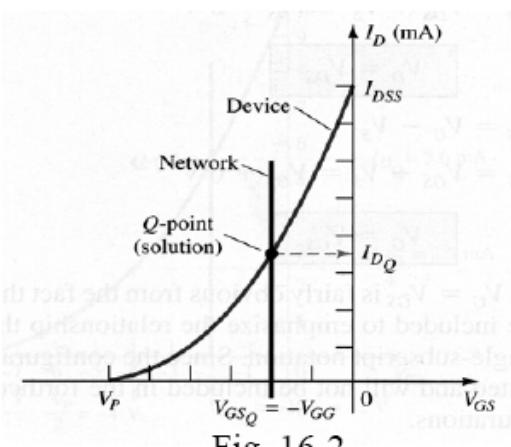

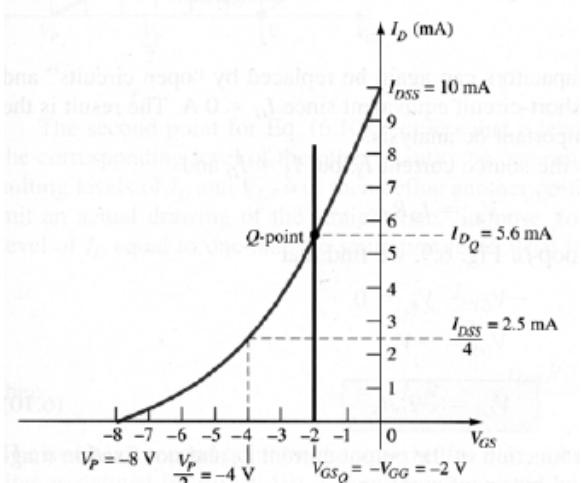

A graphical analysis is shown in Fig. 16-2.

### Example 16-1:

For the circuit of Fig. 16-1 with the following parameters:  $I_{DSS} = 10 \text{ mA}$ ,  $V_P = -8 \text{ V}$ ,  $V_{DD} = +16 \text{ V}$ ,  $V_{GG} = 2 \text{ V}$ ,  $R_G = 1 \text{ M}\Omega$ , and  $R_D = 2 \text{ k}\Omega$ , determine the following:  $V_{GSQ}$ ,  $I_{DQ}$ ,  $V_{DS}$ ,  $V_D$ ,  $V_G$ , and  $V_S$ .

**Solution:**

From Fig. 16-3:

$$V_{GSQ} = -V_{GG} = -2V, \text{ and } I_{DQ} = 5.6 \text{ mA}.$$

$$V_{DS} = V_{DD} - I_D R_D \\ = 16 - (5.6)(2k) = 4.8V.$$

$$V_D = V_{DS} = 4.8V.$$

$$V_G = V_{GS} = -2V.$$

$$V_S = 0V.$$

Fig. 16-1

Fig. 16-2

Fig. 16-3

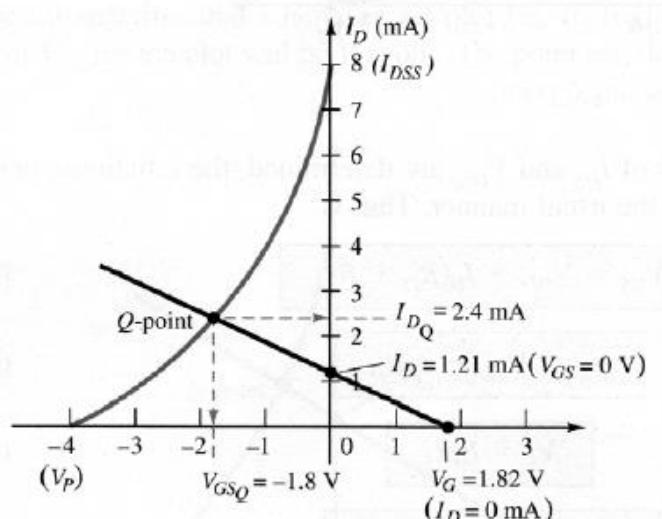

## 2. Self-Bias Configuration:

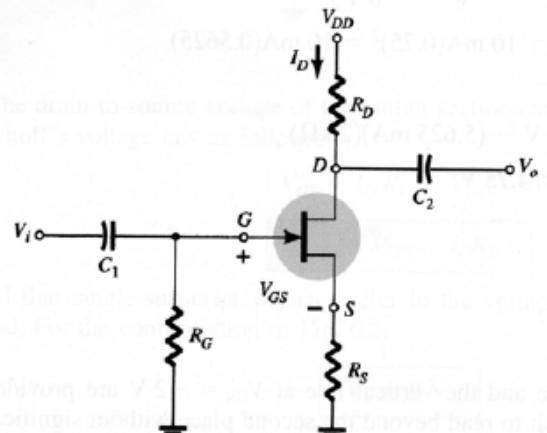

For the circuit of Fig. 16-4,

$$I_G \approx 0A,$$

$$\text{and } V_{R_G} = I_G R_G = 0V.$$

$$I_S = I_D,$$

$$\text{and } V_{R_S} = I_D R_S.$$

For the input circuit,

$$-V_{GS} - V_{R_S} = 0,$$

$$\text{and } V_{GS} = -I_D R_S$$

From Shockley's equation:

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

For the output circuit,

$$V_{DD} - V_{R_D} - V_{DS} - V_{R_S} = 0,$$

$$\text{and } V_{DS} = V_{DD} - I_D (R_D + R_S)$$

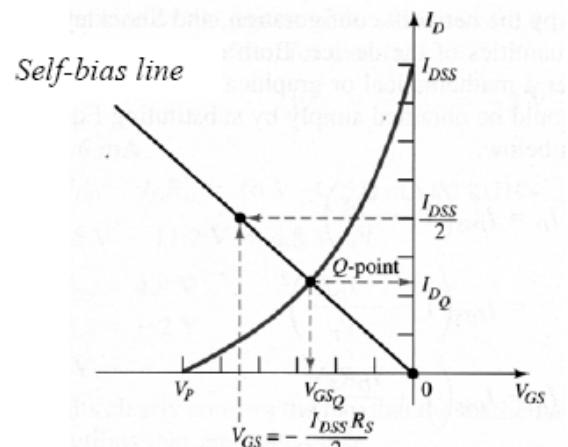

A graphical analysis is shown in Fig. 16-5.

Fig. 16-4

Fig. 16-5

### Example 16-2:

For the circuit of Fig. 16-4 with the following parameters:  $I_{DSS} = 8 \text{ mA}$ ,  $V_P = -6 \text{ V}$ ,  $V_{DD} = +20 \text{ V}$ ,  $R_G = 1 \text{ M}\Omega$ ,  $R_S = 1 \text{k}\Omega$ , and  $R_D = 3.3 \text{ k}\Omega$ , determine the following:  $V_{GSQ}$ ,  $I_{DQ}$ ,  $V_{DS}$ ,  $V_G$ ,  $V_S$ , and  $V_D$ .

**Solution:**

Choosing  $I_D = 4 \text{ mA}$ , we obtain

$$V_{GS} = -I_D R_S = -(4 \text{ mA})(1 \text{k}\Omega) = -4 \text{ V}.$$

At the Q-point (see Fig. 16-6):

$$V_{GSQ} = -2.6 \text{ V}, \text{ and } I_{DQ} = 2.6 \text{ mA}.$$

$$V_{DS} = V_{DD} - I_D (R_D + R_S) \\ = 20 - (2.6 \text{ mA})(1 \text{k}\Omega + 3.3 \text{k}\Omega) = 8.82 \text{ V}.$$

$$V_G = 0 \text{ V}, \text{ and } V_S = I_D R_S = (2.6 \text{ mA})(1 \text{k}\Omega) = 2.6 \text{ V}.$$

$$V_D = V_{DD} - I_D R_D = 20 - (2.6 \text{ mA})(3.3 \text{k}\Omega) = 11.42 \text{ V},$$

$$\text{or } V_D = V_{DS} + V_S = 8.82 + 2.6 = 11.42 \text{ V}.$$

Fig. 16-6

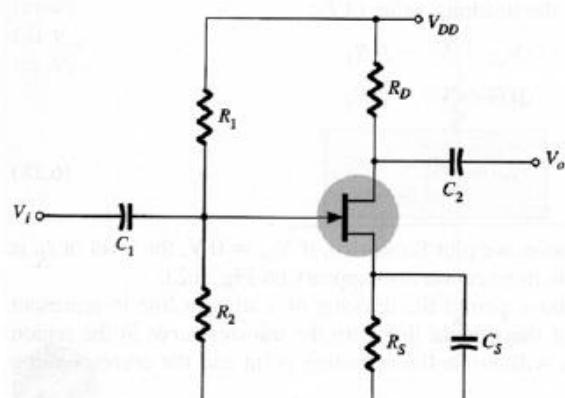

### 3. Voltage-Divider Bias Configuration:

For the circuit of Fig. 16-11,

$$I_G \approx 0A \Rightarrow I_{R_1} = I_{R_2},$$

and

$$V_G = \frac{V_{DD} \cdot R_2}{R_1 + R_2}.$$

For the input circuit,

$$V_G - V_{GS} - V_{R_S} = 0,$$

$$V_{R_S} = I_S R_S = I_D R_S,$$

and

$$V_{GS} = V_G - I_D R_S$$

Fig. 16-11

From Shockley's equation:

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

For the output circuit,

$$V_{DD} - V_{R_D} - V_{DS} - V_{R_S} = 0,$$

and

$$V_{DS} = V_{DD} - I_D (R_D + R_S)$$

A graphical analysis is shown in Fig. 16-12.

Fig. 16-12

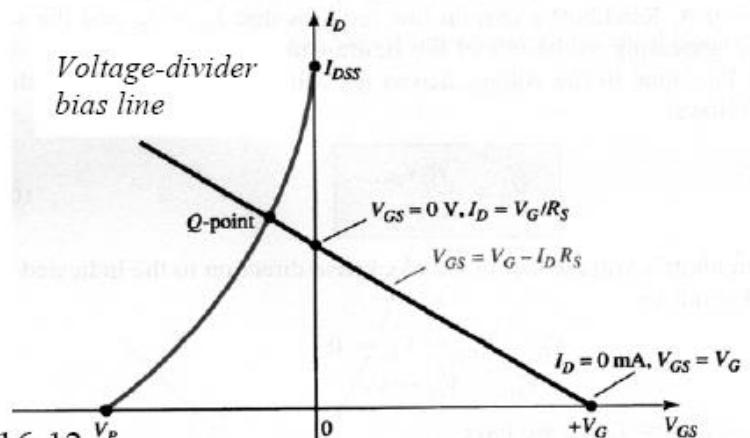

#### Example 16-5:

For the circuit of Fig. 16-11 with the following parameters:  $I_{DSS} = 8 \text{ mA}$ ,  $V_P = -4 \text{ V}$ ,  $V_{DD} = +16 \text{ V}$ ,  $R_1 = 2.1 \text{ M}\Omega$ ,  $R_2 = 270 \text{ k}\Omega$ ,  $R_D = 2.4 \text{ k}\Omega$ , and  $R_S = 1.5 \text{ k}\Omega$ , determine the following:  $V_{GSQ}$ ,  $I_{DQ}$ ,  $V_D$ ,  $V_S$ ,  $V_{DS}$ , and  $V_{DG}$ .

**Solution:**

$$V_G = \frac{V_{DD} \cdot R_2}{R_1 + R_2} = \frac{(16)(270k)}{2.1M + 270k} = 1.82V.$$

$$V_{GS} = V_G - I_D R_S = 1.82 - I_D (1.5k),$$

when  $I_D = 0 \text{ mA}$ :  $V_{GS} = 1.82 \text{ V}$ , and

$$\text{when } V_{GS} = 0 \text{ V}: I_D = \frac{1.82}{1.5k} = 1.21 \text{ mA}.$$

At the  $Q$ -point (see Fig. 16-13):

$$V_{GSQ} = -1.8 \text{ V}, \text{ and } I_{DQ} = 2.4 \text{ mA}.$$

Fig. 16-13

$$V_D = V_{DD} - I_D R_D = 16 - (2.4m)(2.4k) = 10.24V.$$

$$V_S = I_D R_S = (2.4m)(1.5k) = 3.6V.$$

$$V_{DS} = V_{DD} - I_D (R_D + R_S) = 16 - (2.4m)(2.4k + 1.5k) = 6.64V,$$

$$\text{or } V_{DS} = V_D - V_S = 10.24 - 3.6 = 6.64V.$$

$$V_{DG} = V_D - V_G = 10.24 - 1.82 = 8.42V.$$

### Example 16-6 (Two Supplies):

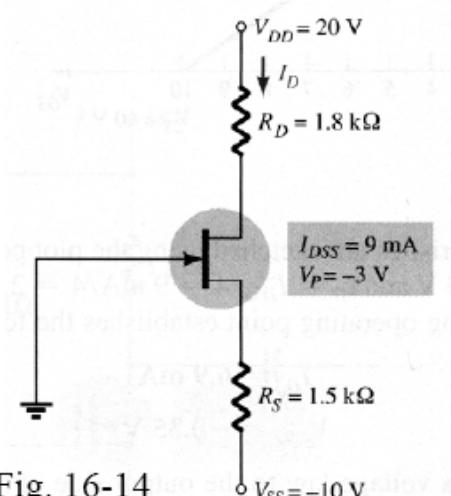

Determine the following for the circuit of Fig. 16-14;

$V_{GSQ}$ ,  $I_{DQ}$ ,  $V_{DS}$ ,  $V_D$ , and  $V_S$ .

Fig. 16-14

**Solution:**

For the input circuit of Fig. 16-14,

$$-V_{GS} - I_S R_S + V_{SS} = 0 \quad (\text{KVL})$$

and  $I_G \approx 0A \Rightarrow I_D = I_S$ ,

$$V_{GS} = V_{SS} - I_D R_S$$

$$V_{GS} = 10 - I_D (1.5k),$$

for  $I_D = 0mA$ ;  $V_{GS} = 10V$ , and

$$\text{for } V_{GS} = 0V; I_D = \frac{10}{1.5k} = 6.67mA.$$

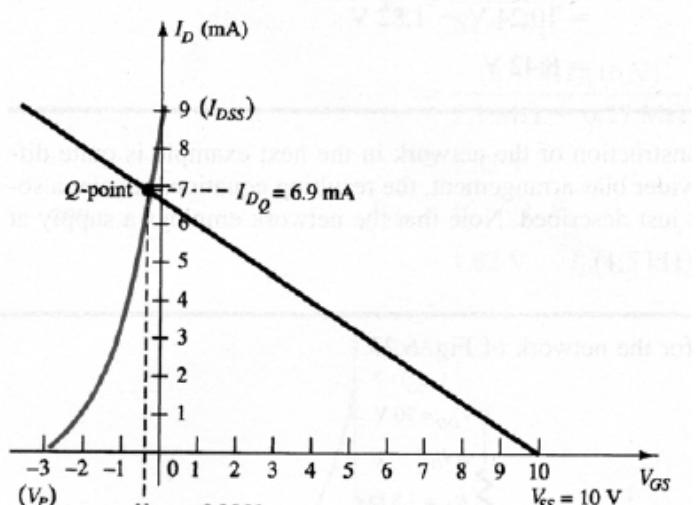

At the  $Q$ -point (see Fig. 16-15):

$$V_{GSQ} = -0.35V, \text{ and } I_{DQ} = 6.9mA.$$

For the output circuit of Fig. 16-14,

$$V_{DD} - I_D R_D - V_{DS} - I_S R_S + V_{SS} = 0,$$

$$V_{DS} = V_{DD} + V_{SS} - I_D (R_D + R_S)$$

$$V_{DS} = 20 + 10 - (6.9m)(1.8k + 1.5k) = 7.23V.$$

$$V_D = V_{DD} - I_D R_D = 20 - (6.9m)(1.8k) = 7.58V.$$

$$V_S = V_D - V_{DS} = 7.58 - 7.23 = 0.35V.$$

Fig. 16-15

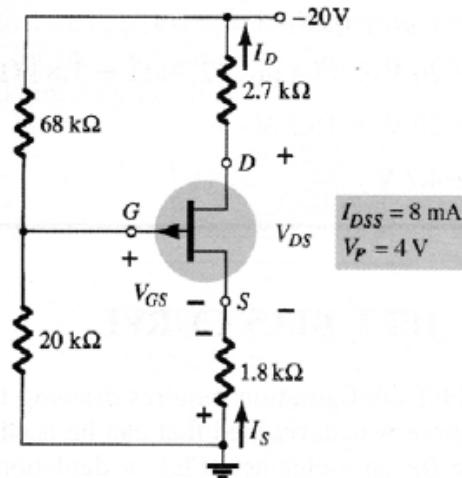

**Example 16-7 (p-channel JFET):**

Determine  $V_{GSQ}$ ,  $I_{DQ}$ , and  $V_{DS}$  for the p-channel JFET of Fig. 16-16.

Fig. 16-16

**Solution:**

$$V_G = \frac{V_{DD} \cdot R_2}{R_1 + R_2} = \frac{(-20)(20k)}{20k + 68k} = -4.55V.$$

$$V_{GS} = V_G + I_D R_S = -4.55 + I_D (1.8k),$$

when  $I_D = 0mA$ :  $V_{GS} = -4.55V$ , and

$$\text{when } V_{GS} = 0V: I_D = \frac{-(-4.55)}{1.8k} = 2.53mA.$$

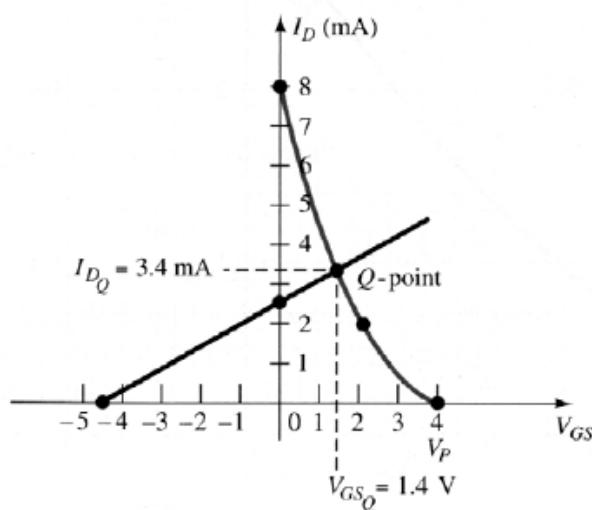

At the  $Q$ -point (see Fig. 16-17):  $V_{GSQ} = 1.4V$ , and  $I_{DQ} = 3.4mA$ .

$$V_{DS} = -V_{DD} + I_D (R_D + R_S) = -20 + (3.4m)(2.7k + 1.8) = -4.7V.$$

Fig. 16-17